intel 12代酷睿引入了异构大小核,amd搞的则是同构大小核,并已在现有的锐龙7040u系列上做了尝试,使用zen4、zen4c的组合,下一代的锐龙8000系列移动版上将升级为zen5、zen5的搭档。

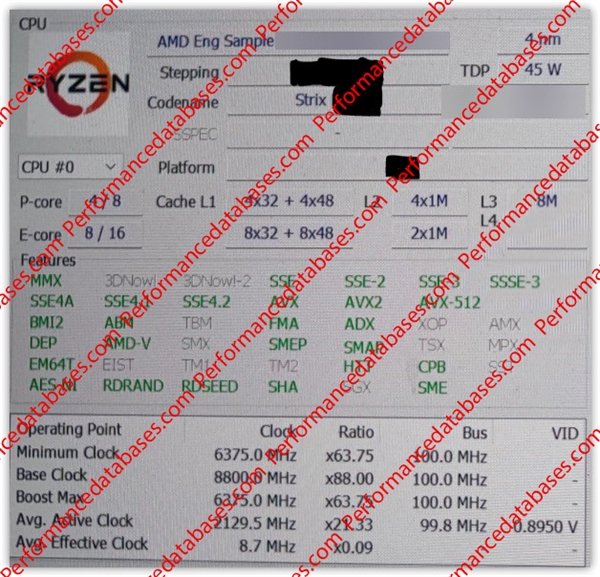

根据此前传闻,代号strix point的锐龙8050系列,将会配备最多4个zen5、8个zen5c核心,同时集成16个cu单元的rdna3.5 gpu、算力翻番到20tops的二代锐龙ai引擎,热设计功耗范围依然是28-54w。

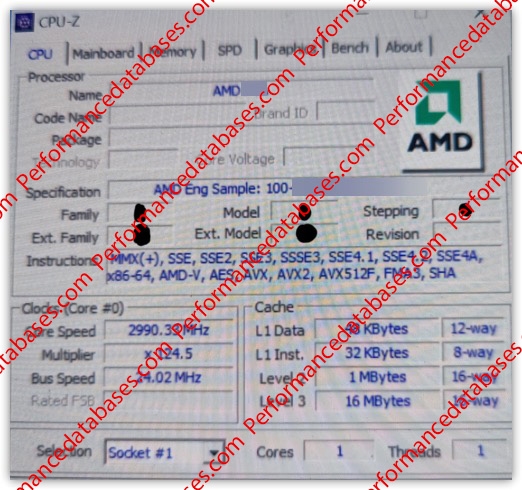

今天在网上看到了疑似锐龙8050处理器的cpu-z、hwinfo截图,可以看到大量基本信息,尤其是4个大核、8个小核,而且都支持多线程技术,都支持avx-512指令集。

这两点,正是intel大小核架构的致命缺陷。

无论zen5还是zen5c,每个核心的一级缓存都是完全一样的,均包括32kb指令缓存、48kb数据缓存,二级缓存则是每个大核单独1mb,每四个小核共享1mb,最后所有核心共享三级缓存(容量检测冲突疑为16mb)。

这种缓存体系,倒是和intel的设计颇为相似。

不过最低6.3ghz、最高8.8ghz的频率,明显是检测错误,毕竟现在还是工程样品阶段。

总之,amd这种同构大小核看起来更加合理一些,性能和功能更完整,也能让系统、更好地适配支持。